-

Notifications

You must be signed in to change notification settings - Fork 38

Commit

This commit does not belong to any branch on this repository, and may belong to a fork outside of the repository.

Added README file of SPI loopback example design.

- Loading branch information

1 parent

0e009b8

commit 256f3e5

Showing

2 changed files

with

34 additions

and

0 deletions.

There are no files selected for viewing

This file contains bidirectional Unicode text that may be interpreted or compiled differently than what appears below. To review, open the file in an editor that reveals hidden Unicode characters.

Learn more about bidirectional Unicode characters

This file contains bidirectional Unicode text that may be interpreted or compiled differently than what appears below. To review, open the file in an editor that reveals hidden Unicode characters.

Learn more about bidirectional Unicode characters

| Original file line number | Diff line number | Diff line change |

|---|---|---|

| @@ -0,0 +1,26 @@ | ||

| # SPI LOOPBACK EXAMPLE | ||

|

|

||

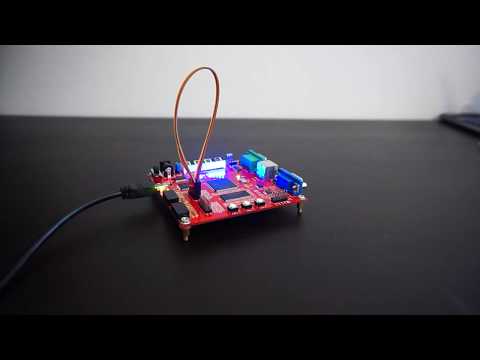

| The SPI loopback example design is for testing data transfer between SPI master and SPI slave over external wires. | ||

| I use it on my FPGA board ([EP4CE6 Starter Board](http://www.ebay.com/itm/111975895262) with Altera FPGA Cyclone IV EP4CE6E22C8 for $45) with few buttons and a seven-segment display (four digit). | ||

|

|

||

| There is video of the SPI loopback example design: https://youtu.be/-TbtB6Sm2Xk | ||

|

|

||

| [](https://youtu.be/-TbtB6Sm2Xk) | ||

|

|

||

| ## Control of SPI loopback example design: | ||

|

|

||

| **Display description (from right on board in video):** | ||

|

|

||

| * Digit0 = value on SPI slave input | ||

| * Digit1 = value on SPI slave output | ||

| * Digit2 = value on SPI master input | ||

| * Digit3 = value on SPI master output | ||

|

|

||

| **Buttons description (from right on board in video):** | ||

|

|

||

| * BTN_ACTION (in mode0) = setup value on SPI slave input | ||

| * BTN_ACTION (in mode1) = write (set valid) of SPI slave input value | ||

| * BTN_ACTION (in mode2) = setup value on SPI master input | ||

| * BTN_ACTION (in mode3) = write (set valid) of SPI slave input value and start transfer between SPI master and SPI slave | ||

| * BTN_MODE = switch between modes (mode0 = light decimal point on digit0,...) | ||

| * BTN_RESET = reset FPGA design |